Ph.D thesis in Computer Science

# Thread Scheduling in Multi-core Operating Systems

How to Understand, Improve and Fix your Scheduler

# Redha GOUICEM

Sorbonne Université Laboratoire d'Informatique de Paris 6 Inria *Whisper Team*

PH.D. DEFENSE: 23 October 2020, Paris, France

# JURY MEMBERS:

| Mr. Pascal Felber, Full Professor, Université de Neuchâtel                     | Reviewer |

|--------------------------------------------------------------------------------|----------|

| Mr. Vivien Quéma, Full Professor, Grenoble INP (ENSIMAG)                       | Reviewer |

| Mr. Rachid Guerraoui, Full Professor, École Polytechnique Fédérale de Lausanne | Examiner |

| Ms. Karine Heydemann, Associate Professor, Sorbonne Université                 | Examiner |

| Mr. Etienne Rivière, Full Professor, University of Louvain                     | Examiner |

| Mr. Gilles Muller, Senior Research Scientist, Inria                            | Advisor  |

| Mr. Julien Sopena, Associate Professor, Sorbonne Université                    | Advisor  |

# ABSTRACT

In this thesis, we address the problem of schedulers for multi-core architectures from several perspectives: design (simplicity and correctness), performance improvement and the development of applicationspecific schedulers. The contributions presented are summarized as follows:

- Ipanema, a domain-specific language dedicated to thread schedulers for multi-core architectures. We also implement a new abstraction in the Linux kernel that enables the dynamic addition of schedulers written in Ipanema.

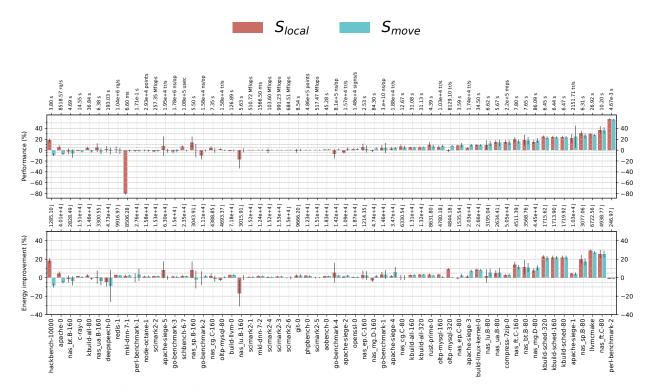

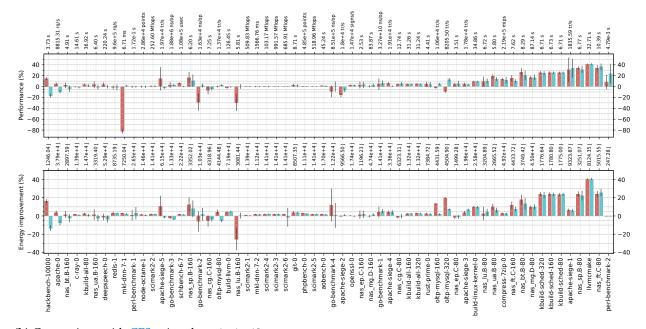

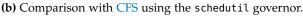

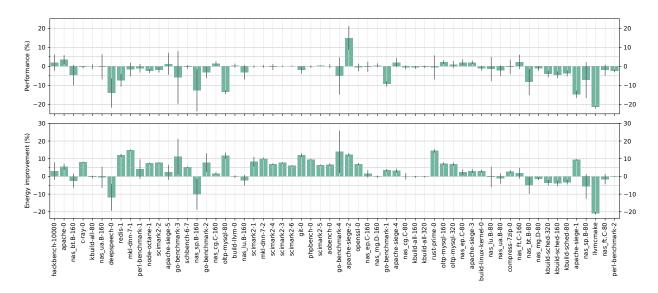

- a series of performance and bug tracking tools. Thanks to these tools, we show that the Linux scheduler, CFS, suffers from a problem related to frequency management on modern processors. We propose a solution to this problem in the form of a patch submitted to the community. This patch allows to significantly improve the performance of numerous applications.

- a scheduler model in the form of a "feature tree". We implement these features independently in order to offer a new fully modular scheduler. This modular scheduler allows us to study exhaustively the different combinations of features, thus paving the way for the development of application-specific schedulers.

# RÉSUMÉ

Dans cette thèse, nous traitons du problème des ordonnanceurs pour architectures multi-coeur en l'abordant sous plusieurs angles: celui de la conception (simplicité et correction), celui de l'amélioration des performances et enfin celui du développement d'ordonnanceurs sur mesure pour une application. En résumé, les contributions présentées sont les suivantes:

- Ipanema, un langage dédié au développement d'ordonnanceurs de processus pour multi-coeur. Nous implémentons également au coeur du noyau Linux une nouvelle abstraction permettant d'ajouter dynamiquement un nouvel ordonnanceur écrit en Ipanema.

- une série d'outils de recherche de bogues de performance. Grâce à ces outils, nous montrons que l'ordonnanceur de Linux, CFS, souffre d'un problème lié à la gestion de la fréquence sur les processeurs modernes. Nous proposons une solution à ce problème sous la forme d'un patch soumis à la communauté. Ce patch permet d'améliorer significativement les performances de nombreuses applications.

- une modélisation des ordonnanceurs sous forme d'un "feature tree". Nous implémentons ces fonctionnalités de façon indépendantes afin de proposer un nouvel ordonnanceur entièrement modulaire. Cet ordonnanceur modulaire nous permet d'étudier exhaustivement les différentes combinaisons de fonctionnalités ouvrant ainsi la voie au développement d'ordonnanceurs spécifiques à une application donnée.

#### ACKNOWLEDGMENTS

Although this thesis bears my name, it is the result of four years of collaborations, discussions and support from fellow researchers, colleagues, friends and family. Research is not the work of solitary individuals but a collaborative enterprise carried out at one's desk, but also during coffee breaks or family dinners. Without further ado, let's thank everyone that was involved in the making of this work.

First, I would like to thank the reviewers, Pascal Felber and Vivien Quéma, for the time they dedicated to carefully reading and evaluating this thesis. I would also like to thank the examiners, Rachid Guerraoui, Karine Heydemann and Etienne Rivière, for accepting to be part of this jury.

This thesis would not have been possible without the guidance and supervision of Gilles Muller and Julien Sopena. Gilles, your expertise in writing papers and bringing the right people together has made this thesis easier than it could have been. I will strive to maintain the rigor in clearly expressing one's ideas that I learned from working with you. Despite the difficult circumstances of the last two years, you were always there and available when I needed help. Julien, you are one of the people that sparked my interest for systems and for research. Working with you every day has been a pleasure, with its share of ideas, each one crazier than the other, but always relevant. I will never be grateful enough for all the things I learned from you, as a scientist and as a human being. A huge thanks to both of you for these four exciting years. You both taught me how to make good systems research and I hope I will live up to your expectations.

I would also like to address a special thanks to Julia Lawall who was not officially my advisor, but still tremendously helped me improve my writing and critical thinking during these four years.

Another special thanks to my co-authors who accompanied me in all this work, Baptiste Lepers, Jean-Pierre Lozi and Nicolas Palix. It has been great to work with each one of you and share all these productive discussions that improved the quality of my work.

The life of a Ph.D. student can be stressful and make you want to give up. When these times arrive, having a cohesive group of people around you is of the utmost importance. This spirit of cohesion is particularly powerful at the LIP6, and more particularly among the three teams I spent most of my time with, Whisper, Delys and MoVe. When I started my Ph.D., I was welcomed by extraordinary people that made my integration easy. I would really like to thank Antoine, Gauthier and Damien who have been mentors for me and many other students I think. I hope I was as good a teacher to new students as you were to me.

I would also like to thank all the other Ph.D. students and interns that I had the pleasure to share my days with: Alexandre, Arnaud, Bastien, Cédric, Célia, Daniel, Darius, Denis, Dimitrios, Florent, Francis, Gabriel, Guillaume, Hakan, Ilyas, Jonathan, Laurent, Lucas, Ludovic, Lyes, Marjorie, Maxime, Pierre, Saalik, Vincent, Yoann.<sup>1</sup>

I also particularly appreciated the good atmosphere between senior researchers and students. I would like to thank all of them for the knowledge they passed on to me as teachers and/or as colleagues. To Jonathan, Luciana, Marc, Pierre, Pierre-Évariste and Swan, thanks for everything.

A special thanks to Karine Heydemann who helped me choose which master to apply to when I was a bit lost. I still remember that discussion from nearly 7 years ago now, and I am thankful for it.

In addition to all my friends from the lab, I would also like to thank the other ones that had no idea whatsoever of what *research in computer science* meant but still supported me. Liazid, Manil, Sami, in addition to the laughs, I really know that if I need help in any matter, you would be among the first ones to answer, and I am grateful for that. Thanks to all my teammates from the LSC Handball, with whom we kept a strong bond a team spirit, be it in victory or defeat. Without you, I might have become a little bit crazy at times.

Another special thanks to Ilyas and Maxime for all these moments of laughs and computer science. I am happy to count you among my friends since we met on the benches of University.

And last, but not least, I would like to thank my family for their unwavering support since always. Mom, Dad, I will never be able to repay you for all you did for me. You always pushed me to work hard and I am glad I listened to you. To my brothers Djelloul, Hichem, Mourad, and my sister Amel, thank you for helping me become the man I am now and supporting me all these years.

These acknowledgments have proved to be longer and more serious than I initially intended before starting writing. For once, I have tried not to make jokes for more than five minutes straight, and that is a challenge I would probably not have been able to overcome four years ago. Again, thanks to each and every one of you, and if I forgot anyone, please forgive me, it was probably unintentional.

<sup>1</sup> In order not to offend anyone, the list is sorted alphabetically :)

# TABLE OF CONTENTS

| 1 | INT | RODUCTION                                     | 1   |

|---|-----|-----------------------------------------------|-----|

|   | 1.1 | Scheduler Development                         | 2   |

|   | 1.2 | Performance Enhancement                       | 3   |

|   | 1.3 | Application-Specific Schedulers               | 3   |

|   | 1.4 | Outline                                       | 4   |

| 2 | THE | READ SCHEDULING                               | 5   |

|   | 2.1 | Execution Entities                            | 5   |

|   | 2.2 | Hardware Resources                            | 6   |

|   | 2.3 | Thread Scheduling                             | 10  |

|   | 2.4 | Scheduling in the Linux Kernel                | 18  |

|   | 2.5 | General-Purpose Operating System Schedulers   | 24  |

|   | 2.6 | User-Level Schedulers                         | 36  |

|   | 2.7 | Hypervisor Schedulers                         | 39  |

|   | 2.8 | Conclusion                                    | 41  |

|   |     |                                               |     |

| 3 |     | ITING SCHEDULERS WITH IPANEMA                 | 43  |

|   | 3.1 | The Ipanema Tool Chain                        | 44  |

|   | 3.2 | The Domain-Specific Language Approach         | 45  |

|   | 3.3 | The Ipanema DSL Through Policies              | 50  |

|   | 3.4 | Scheduler as a Kernel Module                  | 54  |

|   | 3.5 | Property Verification                         | 59  |

|   | 3.6 | Evaluation                                    | 62  |

|   | 3.7 | Conclusion                                    | 67  |

| 4 | FRE | QUENCY-INFORMED SCHEDULING DECISIONS          | 69  |

|   | 4.1 | Example of a Performance Bug in CFS           | 69  |

|   | 4.2 | Monitoring and Visualization Tools            | 70  |

|   | 4.3 | Investigating the Performance Bug             | 74  |

|   | 4.4 | Dynamic Frequency Scaling                     | 78  |

|   | 4.5 | Handling Frequency Inversions in CFS          | 86  |

|   | 4.6 | Evaluation                                    | 88  |

|   | 4.7 | Discussion                                    | 102 |

|   | 4.8 | Conclusion                                    | 103 |

| 5 | FEA | TURE-ORIENTED SCHEDULER ANALYSIS              | 105 |

|   | 5.1 | Feature Analysis of CFS                       | 106 |

|   | 5.2 | Feature Model of a Scheduler                  | 110 |

|   | 5.3 | Feature Evaluation                            | 115 |

|   | 5.4 | Finding the Best Scheduler for an Application | 128 |

|   | 5.5 | Conclusion                                    | 129 |

# X TABLE OF CONTENTS

| 6 | CONCLUSION6.1Scheduler Development6.2Performance Enhancement6.3Application-Specific Schedulers | 131<br>131<br>132<br>133 |

|---|------------------------------------------------------------------------------------------------|--------------------------|

|   | PUBLICATIONS                                                                                   | 135                      |

|   | PRODUCED SOFTWARE                                                                              | 136                      |

|   | BIBLIOGRAPHY                                                                                   | 139                      |

|   | INDEX                                                                                          | 161                      |

|   | ACRONYMS                                                                                       | 162                      |

# INTRODUCTION

In 1951, the **Ferranti Mark 1** and the **UNIVAC** computers were released. These two machines were the first commercialized Turingcomplete machines, able to execute arbitrary programs in the form of punched tapes. Due to their high cost, such machines were only purchased by government agencies, universities and large companies.<sup>2</sup> They executed a large number of different programs, ranging from scientific computing to accounting and national census.

These machines were operated by human operators that loaded code and data into the machine, waited for the computation to complete and retrieved the result. These operators were fundamental in their proper functioning as they ensured the order in which programs should be executed. This was the first form of **scheduling**.

Over the years, with the increased processing power of computers, the cost of human operations became important compared to the computing time. To minimize this cost, computer designers sought to make the scheduler a part of the computer and replace human operators. With the introduction of operating systems (OSs) in 1955, the first software schedulers appeared as a central component of resource management in computers.

Since then, a large number of scheduling algorithms have been developed. They target different workloads and performance objectives. Some server applications need to minimize the latency of their requests, while batch applications need to maximize their throughput. On personal computers and smartphones, interactivity is of the utmost importance for users. Embedded devices, on the other hand, can have strict requirements in terms of quality of service and respect of deadlines.

Schedulers have also been influenced by the evolution of the underlying hardware components of computers, be it central processing units (CPUs), memory or input/output (I/O) devices. The appearance of multi-core processors extended the job of the scheduler. In addition to managing when a program should be executed, it must also choose on which core it should execute. Non-uniform memory access (NUMA) architectures, heterogeneous processors and memory hierarchies further complicate the problem of correctly allocating computing resources. <sup>2</sup> The most popular computer in the 1950s, the **IBM 650**, cost \$500,000 (\$4.76 million as of 2020).

#### 2 INTRODUCTION

The diversification of workloads and user requirements as well as the dazzling evolution of hardware have always been driving forces in the development of schedulers. Combining both the hardware complexity and the software requirements drastically hardens the decision-making process of the scheduler and increases the complexity of its design.

In this Ph.D. thesis, we study thread scheduling and how it affects the performance of applications. We aim at providing new tools for scheduler developers that help them in their work. Our work can be divided into three axes: **scheduler development**, **performance enhancement** and **application-specific schedulers**.

#### 1.1 SCHEDULER DEVELOPMENT

The first axis, **scheduler development**, aims at easing the development of new schedulers in OSs while maintaining a high level of safety. Developing a scheduler is difficult since it involves multiple areas of expertise: scheduling theory, low-level kernel development and hardware architecture. This highly increases the probability of mistakes in the development process. Errors in the scheduling algorithm can lead to important properties being violated unbeknownst to the developer. Implementation mistakes due to the difficulty of developing in an OS kernel are frequent and can cause system crashes. Lastly, a bad knowledge of hardware architecture can lead to inefficient scheduling policies because of factors such as memory latency or heterogeneous computing units.

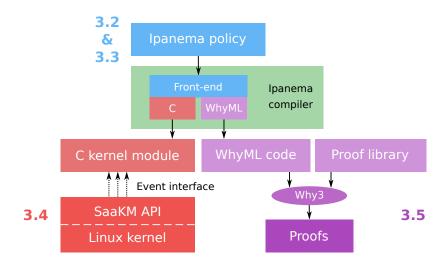

Our objective is to remove the need for the kernel development expertise by providing an easy-to-learn high-level domain-specific language (DSL) that will be compiled into C code usable in Linux. Our compiler contributes to the safety of the code by forbidding illegal operations and by automatically generating code such as lock management. The abstractions of the DSL will also encompass the hardware topology to help developers take that into account. We also want to avoid algorithmical errors by allowing formal verification of scheduling properties to be semi-automatically performed through our DSL.

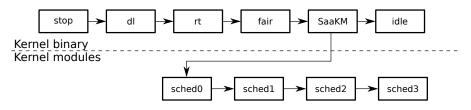

In addition, we also provide a new feature to Linux, Scheduler as a Kernel Module or SaaKM. With this feature, we enable users to insert, at run time, new scheduling policies. Each application can then decide which policy to use. The C code generated by our Ipanema compiler is compatible with SaaKM.

Thanks to SaaKM and our DSL, we develop and test multiple schedulers, such as a simplified version of the Linux scheduler that performs similarly to the original on the set of applications we evaluate. We also develop a version of this scheduler proven to be work-conserving that outperforms the original on some applications.

#### **1.2 PERFORMANCE ENHANCEMENT**

The second axis, **performance enhancement**, aims at helping scheduler developers finding *performance bugs*. These bugs do not cause crashes but silently eat away at performance. They are therefore hard to notice and solve. There are two ways of detecting such bugs: producing a better scheduler that does not suffer from this bug, or using profiling tools that highlight the bug.

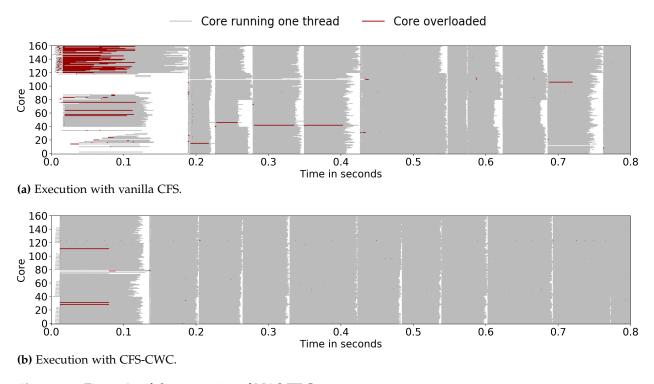

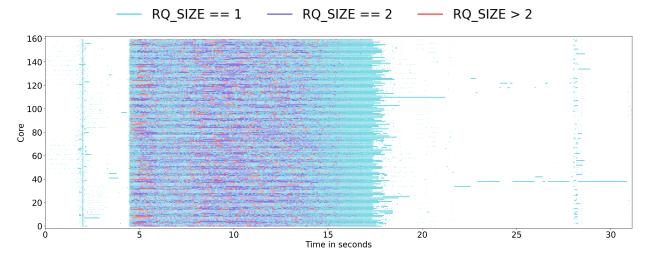

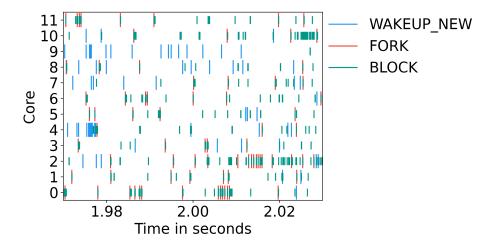

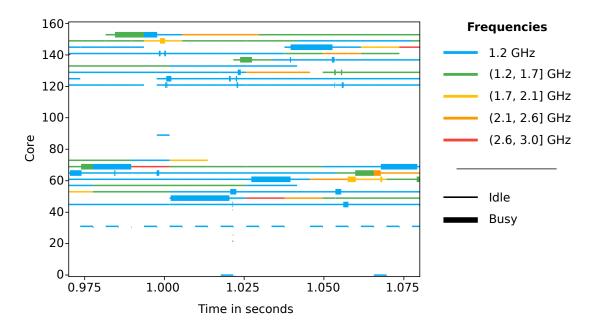

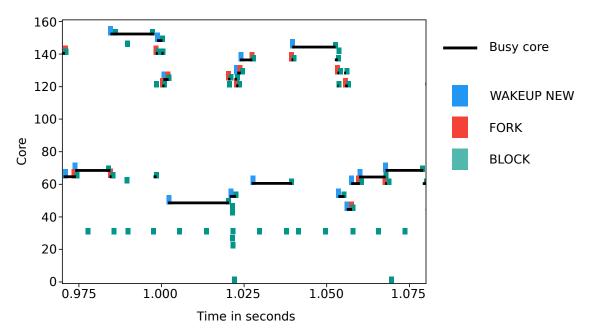

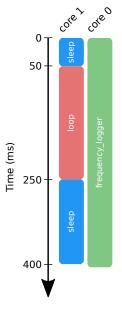

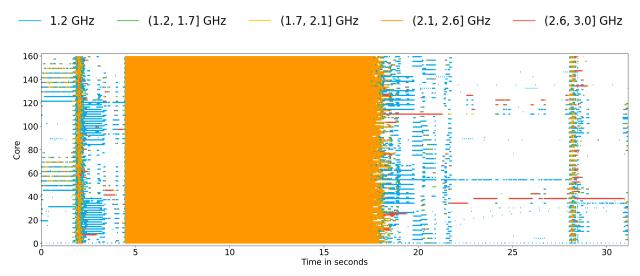

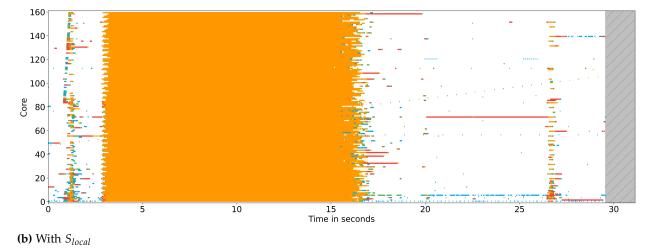

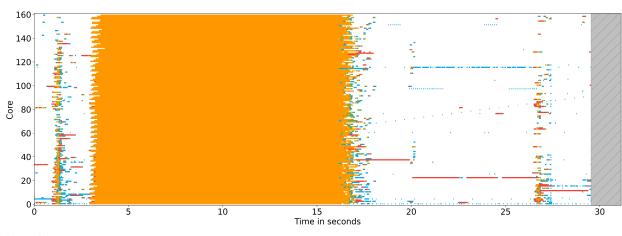

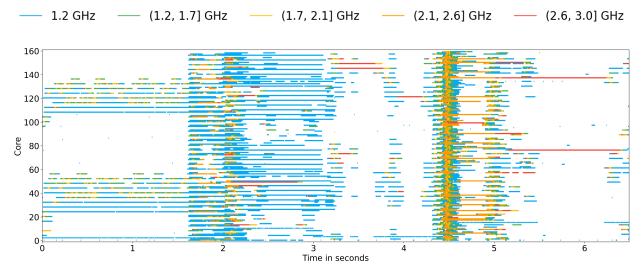

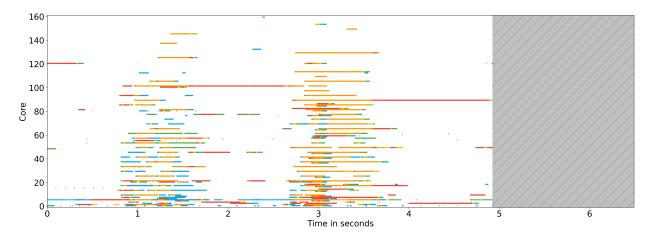

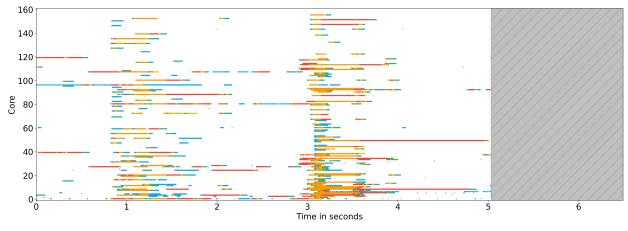

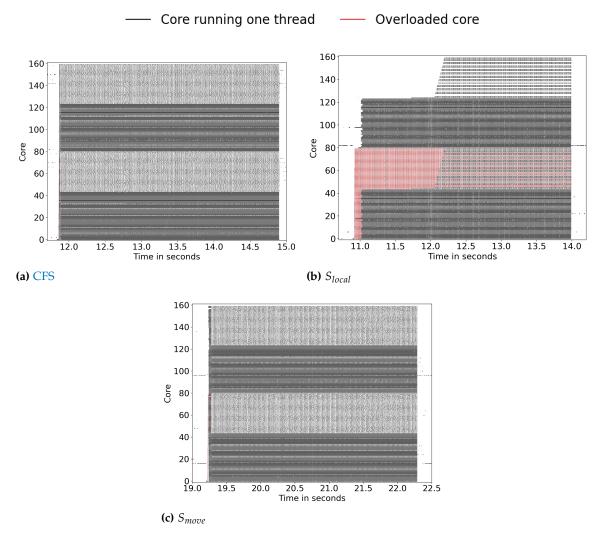

We design monitoring tools to efficiently profile the behavior of schedulers, and visualization tools to easily track performance bugs and identify their origin. These tools enable us to record scheduling events at run time without disturbing application behavior and with a high resolution. They also allow us to visualize specific data such as the CPU usage of each core, their frequency or all scheduling events.

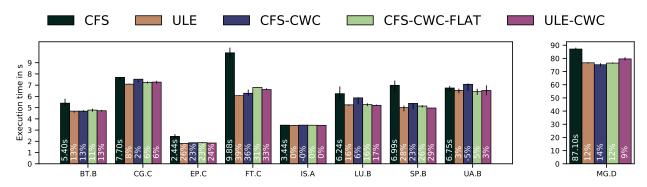

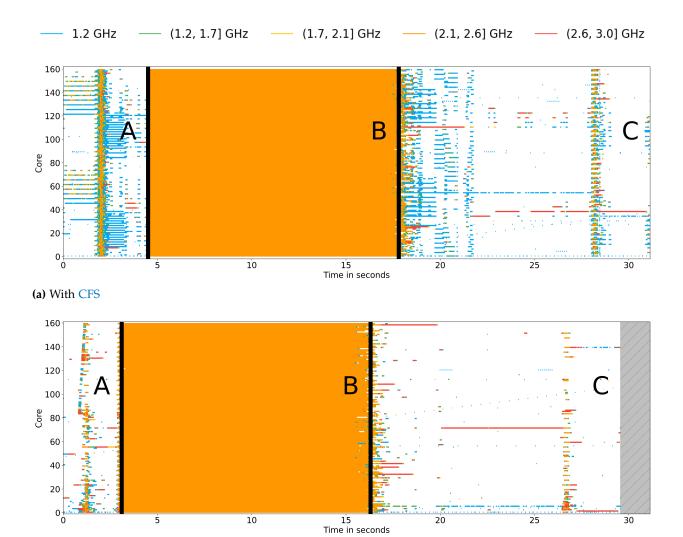

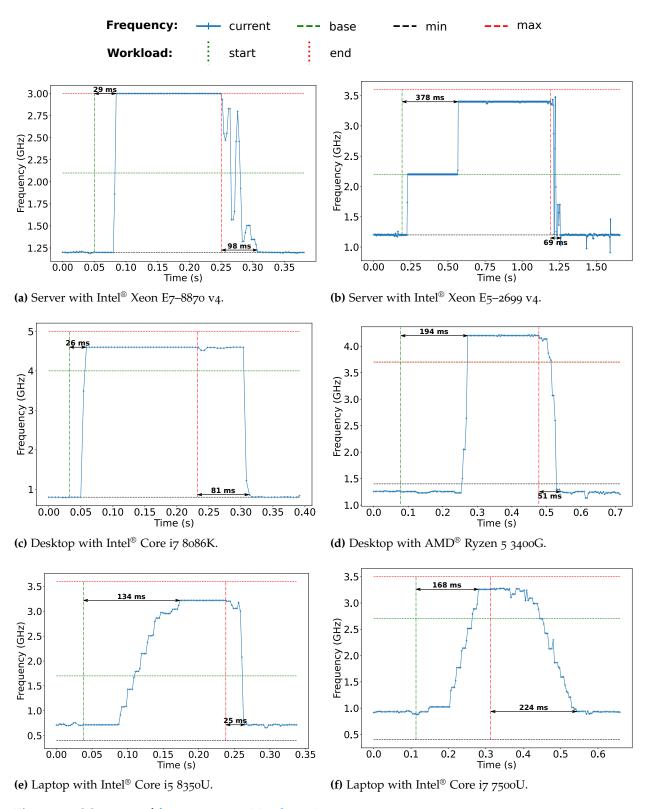

With these tools, we detect a new problem, **frequency inversion**, that stems from modern per-core dynamic frequency scaling and the scheduler unawareness of CPU frequency in its thread placement decisions. This problem triggers situations where high frequency cores are idle while low frequency cores are busy. After finding the root cause of this problem, we propose two solutions for Linux to solve the problem and thoroughly evaluate them. The best solution has been submitted to the Linux community for review.

In addition, we also provide a detailed analysis of the behavior of the frequency scaling algorithm on multiple CPUs. This analysis was possible thanks to our monitoring tools and further strengthens our belief that schedulers must account for the frequency of cores.

#### **1.3 APPLICATION-SPECIFIC SCHEDULERS**

The third and last axis, **application-specific schedulers**, aims at helping software developers use the best possible scheduler for their application instead of always using the default scheduler of the OS. Even though general-purpose schedulers try to be generic and offer good performance for most workloads, they are not able to always offer the *best* performance. This is mainly due to two major problems: the structure and size of their code, and the necessary configuration.

The structure and size problem is prominent in general-purpose schedulers such as Linux's CFS. They tend to be large, with a considerable number of features. These features also tend to be intertwined, be it in terms of code or impact. This increases the likelihood of safety or performance bugs, and hardens the maintenance of the code.

The choice to be generic also creates a fundamental problem: since the expectations of users differ and are sometimes conflicting, it is

#### 4 INTRODUCTION

impossible to always satisfy everyone. To overcome this problem, most general-purpose schedulers are configurable through static configurations at compile time or dynamically at run time. Due to the difficulty of finding the correct configuration for a given workload, most users just use the default values provided by their OS. For more advanced users, there also exist a multitude of user-provided configurations and tips on system administrator forums on the internet.

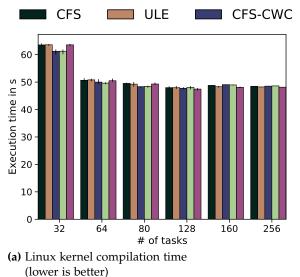

We propose to start building an actual modular scheduler from scratch. To do so, we develop a **feature model** of a scheduler where each feature is implemented independently, making it easy to extend. This model also allows for an evaluation of each feature separately from the others. With such an evaluation, we propose methodologies to find the most adapted features for a given workload. Finally, we propose methodologies to build application-specific schedulers from this data.

#### 1.4 OUTLINE

The remaining of this document is organized in five chapters. Chapter 2 presents the technical background and the state-of-the-art on thread scheduling. It lays off the needed knowledge to understand our contributions. Chapter 3 presents our first contribution, **Ipanema**, a DSL for schedulers. We present the design of the language, its tool chain and an evaluation of multiple policies we implement in Ipanema. Chapter 4 presents our second contribution, the identification of a new problem, frequency inversion, and strategies to solve it. This problem stems from modern implementations of frequency scaling on CPUs and current general-purpose schedulers' behavior during thread placement. We present the problem through a detailed case study and propose two strategies to solve this problem in Linux that we extensively evaluate on multiple machines. Chapter 5 presents our last contribution, a feature model of a thread scheduler. This model is designed with the objective of evaluating scheduler features individually in order to design application-specific schedulers. We present various methodologies that help finding the best suited scheduler for a given application. Finally, Chapter 6 concludes this thesis with a summary of our work and contributions, and discusses future work and perspectives.

# 2

# THREAD SCHEDULING

This chapter aims at defining basic concepts regarding thread scheduling used throughout this thesis, and giving the reader the necessary technical background to understand our contributions. The thread scheduler is the component of a system that manages the allocation of computing resources to software. In this chapter, we first define the hardware and software resources managed by thread schedulers. We then describe in details what are thread schedulers and how they operate. Finally, we describe how thread scheduling is implemented in various systems, with a focus on Linux.

# 2.1 EXECUTION ENTITIES

In operating systems theory, multiple concepts describe software and how it should be executed: threads, processes, tasks, ... Computer scientists tend to mix these terms, usually without loss of meaning in their context. However, in this thesis on scheduling, using one term instead of another would be a mistake and lead to misunderstandings. The following definitions will be used throughout this thesis to avoid such misunderstandings. Figure 2.1 summarizes the hierarchy between each decribed entity.

THREAD. A thread is the entity that executes instructions, and the smallest entity manipulated by the thread scheduler. It is usually represented as an instruction pointer (IP), a stack pointer (SP) and registers. When allocated a computing resource by the scheduler, a thread executes the instruction pointed to by its IP. Threads can be handled at the kernel or at the user level. Kernel threads are managed by the OS's kernel while user threads are manipulated by user level programs such as language runtimes or libraries. Ultimately, user level threads are mapped to kernel threads in order to be scheduled by the OS's kernel. In this thesis, the term thread will be used for kernel threads unless otherwise stated.

**PROCESS.** A process represents a set of resources comprising a memory mapping, file descriptors, sockets, ... A process is used by at least one thread. If multiple threads share a process, communication

|         | Pro | ogram  |        |

|---------|-----|--------|--------|

| Process |     | Proc   | cess   |

| Thread  | l   | Thread | Thread |

Figure 2.1: Illustration of a program with multi-threaded processes.

is simplified thanks to the shared resources. Communicating between processes, on the other hand, is more heavyweight and relies on the use of inter-process communication mechanisms provided by the OS.

**PROGRAM.** A program, or application, is a set of one or more processes, containing one or more threads, that cooperate in order to fulfill a common objective. For example, a web browser that spawns one process per tab is still considered as a single program.

Tasks

The term **task** has various meanings depending on the context. It is used as a synonym to thread or process in Linux. In the Java language, it is either a synonym for thread (when using the Thread class) or a unit of work that can be performed by any thread (when using the Executor interface). Due to this ambiguity, the term task will not be used in this thesis.

#### 2.2 HARDWARE RESOURCES

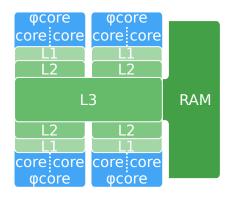

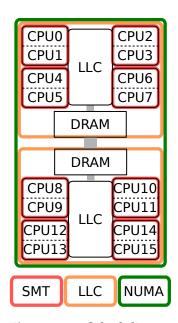

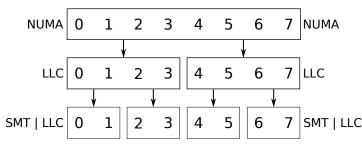

The thread scheduler is the software component that manages the computing units in a system. These computing units have immensely evolved since the beginning of computing. Figure 2.2 shows the hardware topology of a modern machine. In this topology, there are execution units (cores), memory accelerators (caches) and main memory. Some of these components are shared while others are exclusive. All these interactions make the allocation of computing resources a complex job for the scheduler. We present the different hardware components, their possible interactions and impact on the thread scheduler.

# 2.2.1 The Core: an Execution Unit

A core, also called a hardware thread, is the smallest computing unit found in a processor chip. It executes the instructions of a single thread

**Figure 2.2:** A single node 8-core machine, with two threads per physical core ( $\varphi core$ ) and three levels of caches.

of execution at a time. This is the actual resource the thread scheduler manages, allocating it to software threads for given periods of time.

A core is usually composed of a set of registers and computing units. The registers store data used by the running thread as well as metadata used to manage the thread, such as its instruction pointer or its stack pointer. The computing units perform various computations such as arithmetic operations (arithmetic logic unit (ALU)), floatingpoint operations (floating-point unit (FPU)) or address calculations (address generation unit (AGU)).

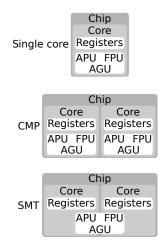

CHIP-LEVEL MULTIPROCESSING. Since the 1950s, a large number of innovations in computer architecture improved the individual performance of cores. Instruction-level parallelism techniques, such as instruction pipelining, speculative execution [19] or out-of-order execution [80], have no impact in terms of scheduling, besides executing instructions more efficiently. Thread-level parallelism techniques, however, change the way the thread scheduler operates by allowing multiple threads to run at the same time. Chip-level multiprocessing (CMP) implements thread-level parallelism by integrating multiple cores into a single chip. Each core is identical and can therefore execute a different thread independently. With CMP, the scheduler can now choose to run multiple threads at the same time.

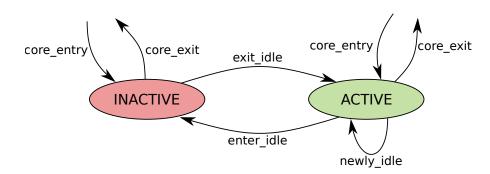

SIMULTANEOUS MULTITHREADING. Early on, computer architects noticed that all computing units were not used at the same time, leading to a waste of computing resources. To solve this, they introduced simultaneous multithreading (SMT) [160]. The idea of SMT is to run multiple threads on the same **physical core** by duplicating part of the hardware, mainly registers. These duplicates are called **logical cores**. For example, Intel<sup>®</sup>'s most common implementation of SMT, Hyper-Threading [85], allows to run two threads per core, i. e. for *n* physical cores, 2*n* logical cores are available. In this thesis, we will use the term **core** to refer to logical cores, since schedulers place threads

**Figure 2.3:** Thread-level parallelism implementations.

#### 8 THREAD SCHEDULING

on this kind of core. SMT has an impact on thread scheduling because some operations will be impossible to perform simultaneously by two cores sharing the same computing units. Figure 2.3 summarizes the difference between CMP and SMT.

ASYMMETRICAL ARCHITECTURES. Some processor chips also feature cores with different capabilities. These **asymmetrical architectures**<sup>3</sup> can have cores specialized in a certain type of computations like video or audio decoding [71, 86, 145]. Another use of this type of architecture is energy management on embedded devices. For example, the ARM<sup>®</sup> big.LITTLE architecture [11] has a set of low power and low performance cores (LITTLE) and a set of more powerful and power-hungry cores (big). Using cores from one or the other set has considerable impact on performance and energy consumption.

The implementation of dynamic voltage and frequency scaling (DVFS) technologies can also be seen as a form of asymmetry. Indeed, if each core can run at a different frequency, they all have a different processing power available. This will be discussed in more details in Chapter 4.

#### 2.2.2 Caches: a Memory Access Accelerator

When cores perform their computations, they usually work with data available in the main memory. Accessing this memory is a frequent operation in software, thus leading researchers to improve memory access efficiency. A widespread way of doing so is to place small hardware caches between cores and main memory. Caches are faster than main memory but are more expensive. The goal is to exploit two properties: temporal locality [182] and spatial locality [109].

**Temporal locality** specifies that recently accessed data has a high probability of being accessed again in the near future. To exploit this property, caches are used to keep recently accessed data close to cores using them.

**Spatial locality** specifies that when a piece of data is accessed, neighboring data has a high probability of being accessed in the near future. To exploit this property, when a piece of data is loaded into a cache, adjacent data is also loaded for future accesses. As a result, computer architects design memory hierarchies with fast and small caches close to cores, and slower but larger caches farther from cores and closer to memory. This is visible in Figure 2.2 with three levels of caches available.

Caches can also be used to easily share data between cores. In our example, there are two levels of caches exclusive to a single physical core (L1 and L2) and one level that is shared between all cores (L3). Sharing is beneficial when multiple cores access the same data, removing the need to load it from main memory again and

<sup>3</sup> Also called heterogeneous architectures. again. However, if all cores use different data, they compete for the same cache locations, leading to data evictions, and subsequent main memory accesses. This phenomenon is called cache thrashing. Cache sharing or thrashing has an impact on scheduling decisions since different thread placements can induce more or less sharing and thrashing.

#### 2.2.3 Main Memory: a Potential Bottleneck

Even though caches reduce the number of memory accesses, main memory is still a critical resource. Some accesses cannot be cached and some access patterns make caching an inefficient optimization. For these reasons, main memory is still a potential performance bottleneck.

SYMMETRIC MULTIPROCESSING. The coupled use of a multi-core design (CMP and/or SMT) and cache hierarchies connected to a single main memory is called symmetric multiprocessing (SMP).<sup>4</sup> These architectures use an *interconnect* to link all their components, from caches to main memory and I/O devices.<sup>5</sup> One main characteristic of these systems is that accessing memory has the same cost, regardless of the core doing the access. These SMP architectures greatly improve performance by allowing multiple threads to run concurrently with fast memory accesses.

With the rising number of cores, the number of requests to main memory has drastically increased. At the same time, technologies behind main memory evolved more slowly than those behind processors. With more than a dozen cores, main memory cannot keep up with the number of requests and respond in an acceptable time.

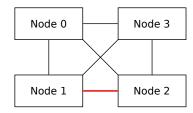

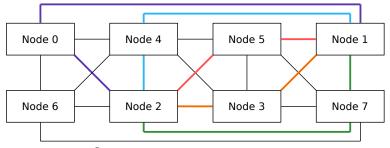

NON-UNIFORM MEMORY ARCHITECTURE. One way to solve this problem is to apply on main memory the same recipe that was applied on cores: duplication. Instead of having a single main memory that serves all cores, the machine is split into **nodes**, as illustrated in Figure 2.4. A node can be seen as an SMP system, with a set of cores, caches and its own main memory. The objective is to limit the number of cores that access the same main memory concurrently. Ideally, each node is a closed system where cores only access the main memory of their node, i. e. **local memory**.

Nonetheless, a system where each node is fully isolated is hardly possible. Some data must be shared between nodes for multiple reasons, including data from the OS or large-scale applications that have threads spanning multiple nodes. Nodes are therefore connected to each other to allow cores on a given node to access the memory of another node, i. e. **remote memory**.

Remote accesses are not as fast as local accesses since they must go through additional interconnections. These non-uniform memory <sup>4</sup> Multiple definitions exist, including or excluding caches, but we will use this one for the remainder of this thesis [43].

<sup>5</sup> The interconnect can be a shared system bus or a point-to-point interconnect.

(a) 4-node Intel<sup>®</sup> Broadwell machine (1 hop).

(b) 8-node AMD<sup>®</sup> Bulldozer machine (2 hops).

**Figure 2.4:** Topologies of two NUMA machines. Shortest routes from node 1 to node 2 are highlighted.

access (NUMA) architectures come in multiple flavors, with different degrees of uniformity between access times. Figure 2.4a shows a fully connected NUMA architecture where all remote accesses roughly take the same time to complete under the same level of contention. Figure 2.4b, on the other hand, shows a topology where nodes are not fully connected. If a thread on node 1 wants to access data on node 2, the shortest routes are two hops long, going through one node on the way. The five possible routes are highlighted in Figure 2.4b. The longer the distance between two nodes, the longer it takes to access memory. The use of such routes can lead to contention on the interconnect, mitigated by routing algorithms implemented in hardware. Software can also help mitigation by placing threads and memory on the best nodes possible.

#### 2.3 THREAD SCHEDULING

We now have a clear picture of the computing resources, i.e. cores, and the entities that use them, i.e. threads. In order to manage these cores and allocate them to threads, we need a component that will handle this job. The thread scheduler is this component. The design of a scheduler can be expressed as the answer to four questions:

- WHICH thread should run?

- WHEN should it run?

- WHERE should it run?

- WHY should it run?

The thread scheduler's job is to answer these four questions. In this section, we first provide some early history of scheduling. We then detail the generic model commonly used to define threads, the ins and outs of each question, and how schedulers answer to these questions.

## 2.3.1 Early History

In the early days of computing, mainframes did not have OSs. Operators manually inserted their programs and data in the form of punch cards or magnetic tapes, waited for the computer to perform all needed computations, and retrieved the results printed by the machine. In the 1950s, as mainframes became more and more fast, the cost of human operations became important compared to the computing time. Pioneers of computing set out to solve this problem by automating these operations: OSs were born.

The first OSs<sup>6</sup> used a **monoprogramming** paradigm, where a single application could run at a time, with no means to switch between applications until their completion. The completion time of a program depends on its own execution time as well as the completion times of the programs running before it. The order in which programs would be scheduled was manually chosen by a human operator.

Later on, in the 1960s, **multiprogramming** OSs made their apparition, with IBM's OS/360 leading the way. The MVT variant of this OS, released in 1964 for the large machines of the System/360 family, introduced time-sharing. This allowed multiple programs to run at the same time, as well as interactive usage of computers. Developers were now able to write programs with a text editor while batch jobs were running in the background. The software component that governs how computing resources are shared between application, the scheduler, was born.

#### 2.3.2 The Thread Model

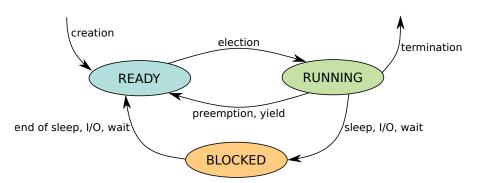

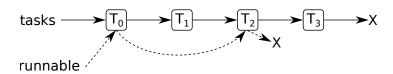

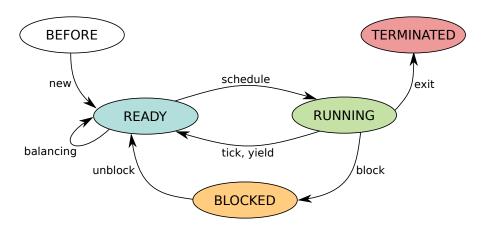

As stated previously, a thread is the smallest schedulable entity in a system. During its lifecycle, it goes through multiple states that depend on the code it is running. It is in a RUNNING state when using a computing resource, READY when waiting for a computing resource, Or BLOCKED when waiting on an external resource such as reading an I/O device. This behavior is best modeled as the finite state machine shown in Figure 2.5. All transitions of this finite state machine can lead to the intervention of the scheduler. Election determines which thread should run next on a core, while preemption or yield determines when a thread should stop using a core. These transitions can be triggered by the application, e.g. by yielding the CPU through a system call, or by the scheduler itself.

<sup>6</sup> The first OS, GM-NAA I/O, was released in 1955 by General Motors for the IBM 704 computer [146].

Figure 2.5: Finite state machine modeling a thread.

<sup>7</sup> Also called cooperative schedulers.

The decision to change the currently running thread can be taken at various times. **Non-preemptive** schedulers<sup>7</sup> are triggered only when the running thread relinquishes the use of the processor, be it due to a blocking operation, e. g. an I/O operation, or a willing yielding, i. e. calling the yield() system call. In this setup, the scheduler only decides which thread should run, but not for how long. This will depend on the selected thread's behavior. This type of scheduler was used in old OSs but was dismissed because malicious or bugged threads could hang the machine by never blocking, e. g. executing an infinite busy loop. However, non-preemptive scheduling presents the benefit of simplicity. Applications do not need to worry about being interrupted, easing the development process. Non-preemptive schedulers are still used in controlled setups such as embedded systems where all running applications are known.

Most modern general-purpose schedulers allow thread **preemption**. This means that the scheduler is not only called when the running thread stops using the processor, but also when the OS wants to. For example, the scheduler can be triggered when the running thread exits a system call or after handling a hardware interrupt. This design gives more opportunities of scheduling out a malicious or bugged thread that would otherwise hog a core. Even in a sane environment, preemption enables the scheduler to schedule a waking up thread if its priority is higher than the currently running thread's priority.

Another usage of preemptive scheduling is the implementation of **time-sharing** policies. In order to allocate the processor to a thread for only a given period of time, time-sharing schedulers usually periodically trigger a timer interrupt. During each interrupt, or **tick**, the scheduler evaluates if the currently running thread should still be scheduled until the next tick. If not, the election mechanism is triggered to choose a new thread to run. This is an essential feature of interactive systems like personal computers or smartphones. It is also essential in shared servers where different clients should be able to use the processing resources fairly.<sup>8</sup>

<sup>8</sup> Fairness is not a synonym for equality, it can be weighted depending on multiple factors.

### 2.3.3 Election

Originally, CPUs only had a single core, and the scheduler was only responsible for deciding **which** thread should run on the core and **when**. Different strategies can be put in place for this purpose, such as fairly assigning the same time to every thread, or prioritize some threads over others. Usually, general-purpose OSs choose fair approaches because the main goal is to provide good performance for every application. However, the behavior of each application is different, and treating each thread equally might not be in the best interest of overall performance.

Applications are traditionally classified into two categories: *I/O-bound* and *CPU-bound*. *I/O-bound* applications frequently perform I/O operations and relinquish using the processor. I/O operations can be accesses to storage or network, or waiting for a keyboard press from the user. These applications usually require to use the CPU frequently but shortly, and aim at low latency. *CPU-bound* applications, on the other hand, tend to mostly use the processor without performing I/O operations. They usually require long consecutive periods of time to use the CPU to minimize the cost of context switching between threads and improve cache usage, and aim at high throughput.

In the real world, applications can exhibit both behaviors: an application can have different phases that are either CPU- or I/O-bound. For example, a web browser is I/O-bound when waiting for user input (e.g. a URL) and CPU-bound when processing the content of a webpage to display it to the user. The duality of these behaviors can also be seen in multithreaded applications where some threads are I/O-bound while others are CPU-bound.

With these two classes of threads in mind, the thread scheduler of a general-purpose OS must try to satisfy all threads equally. This is done through various algorithms and heuristics that, depending on the thread's behavior, determine its needs and the best decision to fulfill them. For example, I/O-bound threads will have a higher chance of being selected than CPU-bound threads because they use the CPU for very short periods of time. However, the number of threads to satisfy and their differing needs make it a hard job for the scheduler to fairly provide the best possible performance for all threads.

In a specific OS, as opposed to a general-purpose OS, fairness is not necessarily a concern. For example, real-time OSs tend to implement unfair strategies to ensure that operations are performed in a timely manner deterministically. For example, the *Electronic Brakeforce Distribution* technology [26] in modern cars computes the force to apply on each wheel of the vehicle depending on multiple factors (force on the pedal, speed, road condition, ...). If this computation is too slow, the data collected by the sensors becomes obsolete, and braking not as efficient as it should have been. Real-time system engineers therefore

#### 14 THREAD SCHEDULING

choose a *deadline* before which the computation must complete at all costs. The thread scheduler of computer systems running such applications does not care for fairness between threads, but instead care for the respect of all deadlines.

#### 2.3.4 Placement Management

With multi-core architectures, the thread scheduler must also decide **where**, i. e. on which core, a thread should be executed. This new role adds a whole new complexity to thread scheduling, not only because of these new resources to allocate, but also because of the way in which these resources are interconnected. While cores are exposed as independent resources, they still share hardware at different levels, as described in Section 2.2. These resources include computing resources (SMT), caches, main memory and interconnects. When shared by multiple cores, they are subject to contention. Scheduling decisions directly affect the level of contention on every shared component, placing the thread scheduler at the center of resource management.

Resolving the contention problems of these modern architectures at the scheduler level is done in various ways. One way to solve cache contention is to spread threads across cores sharing the minimum number of caches. This will improve the performance of the applications if threads a thrashing each other's data from the caches. However, when threads share data, doing this could reduce the performance and increase the contention on interconnects and memory controllers. This is due to the fact that data would need to be accessed from memory and the traffic due to cache coherence protocols will increase. Similarly, taking advantage of shared caches in a collaborative application might induce contention on the shared SMT hardware, caches, as well as on the local memory controller.

As is the case with time management, placement management must take advantage of multiple hardware technologies aimed at improving performance, with each improvement potentially deteriorating the performance of another piece of hardware. General-purpose OSs must find the best compromise in order to achieve the best overall performance for all running applications.

Heterogeneous architectures also introduce complexity in terms of thread placement. As presented earlier, asymmetrical architectures have cores with different capabilities, and the scheduler must take them into account. For example, on ARM<sup>®</sup> big.LITTLE architectures, the scheduler must decide to favor either performance or energy saving by placing threads on big or LITTLE cores.

For all these reasons, thread placement is an essential component of the scheduler. It is also a very complex one due to its particularly close relation to hardware. As described on various occasions previously, a scheduler ensures a set of properties that affects its performance. A scheduler developer must ask himself **why** he is developing a scheduler to deduct which properties must be enforced. A property is not inherently good or bad, it is the targeted applications and use cases that make a property good or bad for a given setup.

LIVENESS. **Liveness**<sup>9</sup> ensures that a thread requiring computing resources, i. e. a READY thread, will get access to a computing resource in finite time [148]. This is desirable in general-purpose OSs where no thread should be starved from using the processor. Note that this does not mean that the application necessarily makes progress, as poorly coded applications might get stuck in busy loops or livelocks. From the point of view of the scheduler, this is still considered as progress.

FAIRNESS. Fairness ensures that all threads are given the same amount of computing resources. Again, it is usually a desirable property in a general-purpose OS scheduler. The level of fairness between threads can also have a large impact on performance. Being "too" fair would mean context switching between threads more frequently, thus wasting valuable computing resources. Fairness should not be confused with equality: all threads must not have the same allocated CPU time, it also depends on the thread's requirements.

Fairness can be provided by **proportional share** schedulers such as Fair Share Schedulers [76, 92] or Lottery Scheduling [178]. These schedulers are largely inspired or influenced by network queueing algorithms [15, 46]. Patel *et al.* [135] improve fairness with scheduler-cooperative locks. Zhong *et al.* [194] do a similar thing in virtualized environments.

**PRIORITY.** Some systems schedule threads by strict **priority**: the thread with the highest priority must run before all other threads. With this type of scheduler, high priority threads have a high probability of running quickly and perform their work uninterrupted by other threads. In these priority-based schedulers, when multiple threads share the same priority, there must be a way to select which one should run. This choice is usually done in a round robin fashion.

Unix-based systems expose priority through the *nice* value, although it is sometimes only used as a parameter in proportional share schedulers. Priority-based scheduling is also proposed for hard or soft real-time systems [74, 104, 154].

**RESOURCE SHARING.** On systems with SMP or NUMA architectures, contention on shared hardware can quickly become a perfor<sup>9</sup> Also called freedom from starvation.

mance bottleneck. To address this issue, schedulers can take the usage of such shared resources into account and schedule threads in a way that minimizes contention. This can be done by avoiding to run two threads that use the same hardware resource at the same time, or by placing threads on distant cores to avoid resource sharing altogether. On the other hand, sharing can be beneficial in some cases. For example, two threads working on the same data benefit from sharing caches, thus diminishing the number of memory accesses performed.

Multiple approaches were proposed regarding different shared resources. Systems featuring SMT have been studied to minimize contention due to this technology [7, 134, 161]. Various work focus on memory contention [9, 155, 188] or shared caches [57, 58]. Other approaches propose different heuristics to detect and avoid contention or use beneficial sharing [120, 162, 163, 192, 195].

INTERACTIVITY. A large number of applications require good performance in terms of **latency** or **interactivity**. For example, user interfaces must react quickly to inputs so that the end user does not notice lag. Databases and servers also have request latency requirements to fulfill in order to be responsive.

Automated approaches that estimate the requirements of applications on the fly based on system observations have been proposed [14, 42, 50, 147, 164]. Redline [190] improves the performance of interactive applications by allowing users to specify requirements to the scheduler without modifying the application. Other solutions propose to provide an application programming interface (API) to applications so that they can communicate their requirements to the scheduler at run time [3, 101, 150].

WORK CONSERVATION. On multi-core systems, another interesting property is **work conservation**. A work-conserving scheduler leaves no core idle if there is a READY thread available on the system. This can be seen as either a good or bad property, even from a purely performance-oriented point of view. Using all cores might increase contention on shared resources [56], but it also increases the computing power available for threads. The benefits of this property is application-specific. Most general-purpose schedulers try to achieve work conservation, although not necessarily at all times due to the induced scheduling cost.

**REAL-TIME.** In real-time contexts, a usually desirable property is the **respect of deadlines**. Real-time applications perform tasks that must complete before a given time called a *deadline*. Real-time scheduling algorithms, such as Earliest Deadline First (EDF) [110] or deadline monotonic scheduling [12] enforce deadlines for applications if the system is sized correctly, i. e. it is possible to run all applications without exceeding deadlines.

ENERGY. Embedded systems could also require to keep a **low energy consumption**. This can be solved at the scheduler level at the expense of performance. This type of systems can also disable clock ticks to save energy on idle cores. The scheduler must therefore be adapted to work on these **tickless** systems.

Prekas *et al.* [141] improve energy proportionality, i. e. the quantity of energy consumed compared to the work performed. Merkel *et al.* [120] use co-scheduling and dynamic voltage and frequency scaling (DVFS) to improve performance and save energy.

PAIRING PROPERTIES. Some of these properties are contradictory with one another. For example, it is not possible to be work-conserving and to lower energy consumption by not using some cores. Similarly, fairness can be unwanted in a real-time context, where respecting deadlines is of the utmost importance.

Conversely, pairing some properties can be highly beneficial for some workloads. In a real-time context, reducing contention over shared resources can allow threads to respect their deadlines more easily [18].

#### 2.3.6 The Place of Thread Scheduling in a Computer System

The operating system is the interface between hardware resources and software. It is responsible for the management and allocation of hardware resources to software that require them. Those resources include, but are not limited to, memory devices, input/output devices and cores. OSs are commonly divided into two parts, kernel and user spaces, each having its own address space.<sup>10</sup> The boundary between both spaces depends on the chosen kernel architecture: a monolithic design will embed all OS services in kernel space, while a microkernel approach will push the maximum number of services away from kernel space towards user space.

Thread scheduling can be performed at different levels of the OS, and even outside of it. Most general-purpose OSs, such as Linux, FreeBSD or Windows, implement scheduling at the kernel level. Another approach would be to implement it as a user space service of the OS. Thread scheduling can also be done by user applications themselves. This is the case with multiple threading libraries like OpenMP [44]. Some languages, most notably Go [48], expose lightweight threads (goroutines in Go) that are scheduled by the language's runtime. These user level schedulers either exploit capabilities offered by the underlying OS scheduler to manage thread <sup>10</sup> Single address space approaches exist, such as the Singularity OS [79]

"A concept is tolerated inside the microkernel only if moving it outside the kernel, i.e., permitting competing implementations, would prevent the implementation of the system's required functionality." — Liedtke Jochen [107] ordering and placement, or add a new layer of scheduling above the OS scheduler.

Finally, in a similar way, virtualized environments can also add a layer of thread scheduling. The hypervisor allocates a number of virtual CPUs (vCPUs) to each hosted virtual machine (VM), and each VM sees these vCPUs as physical CPUs. Therefore, the hypervisor schedules vCPUs on physical CPUs, while each VM schedules threads on vCPUs.

From these layered schedulers arise multiple problems. First, one layer does not necessarily know that other layers exist, most notably with virtualization. This means that schedulers in VMs may take decision with incorrect informations relayed by the hypervisor unknowingly. Second, each layer may take decisions independently, leading to conflicts between each layer. These challenges make it difficult to achieve the best possible performance, with multiple schedulers acting without communication between them.

#### Cluster scheduling

Computation can also be managed at the cluster level. The goal of this cluster scheduler is to place jobs on machines. Each machine will then perform scheduling locally. This topic will not be covered since it is out of the scope of this thesis.

#### 2.4 SCHEDULING IN THE LINUX KERNEL

With this understanding of the general principles of thread scheduling, we can now dive into the description of production schedulers used every day. In this thesis, all contributions are implemented in the open source GNU/Linux environment. More precisely, the scheduler subsystem is located in the Linux kernel. We provide a tour of this subsystem in order to better understand the contributions of this thesis.

#### 2.4.1 Overview

The Linux kernel, and the distributions that use it, are Unix-like systems that implement a large part of the Portable Operating System Interface (POSIX) [81] standards. More precisely, in terms of thread scheduling, the POSIX.1 standard defines scheduling policies, thread attributes and system calls that allow users to interact with the scheduler.

SCHEDULING POLICIES. The standard requires three scheduling policies, i. e. scheduling algorithms, to be implemented: SCHED\_FIF0, SCHED\_RR and SCHED\_OTHER. Through specific system calls, threads

can change from one policy to another during their execution. As their name suggests, SCHED\_FIF0 and SCHED\_RR respectively implement First-In First-Out and round-robin algorithms to select which thread to run. They are mainly used for real-time applications. The SCHED\_0THER policy, is implementation-defined and can be whatever the OS developers want it to be. It is usually used to implement a fair policy in general-purpose OSs. More details on these policies will be provided in the following sections.

THREAD ATTRIBUTES. Two mandatory thread attributes are defined by the POSIX standard: the thread **priority** and the **nice** value. These two terms have very similar meanings and are often confused. However, they define two different concepts that are important to dissociate.

**Priority** reflects the importance of a thread, and therefore the relative urgency of a thread to be scheduled compared to others. The higher the priority, the most chance a thread has to run. Priority can evolve over time, as seen fit by the scheduler, to reflect a thread's behavior. For example, as previously stated, a widespread decision is to raise the priority of I/O-bound threads while reducing the priority of CPU-bound ones.

The **nice** value is a handicap a thread can impose on itself regarding the use of the processing resources. A high nice value means that the thread is not in great need of using the processor and prefers to let other threads use it instead. This value is thus a hint given by threads to the scheduler that specifies their scheduling needs. Threads can increase their *nice* value to communicate their lack of urgency to use the processor to the kernel.<sup>11</sup>

SYSTEM CALLS. The interaction between threads and the scheduler is also driven by multiple system calls. The only mandatory one directly related to scheduling is sched\_yield(). It allows a RUNNING thread to relinquish its ownership of the processor resource. Other system calls transition a thread to a BLOCKED state, most notably those accessing I/O devices such as storage or network devices. Such system calls are defined by the POSIX standards, but not directly as scheduler-related system calls. Their impact on scheduling is more a side effect needed for performance than a direct interaction. If they did not trigger scheduling events, BLOCKED threads would keep the ownership of the processor even though they cannot use it. There are also other system calls that remain optional, such as the ones used to move from one scheduling policy to another or to manage real-time policies. <sup>11</sup> On most systems, any thread can increase its nice value, but decreasing it requires elevated privileges.

Figure 2.6: Thread states in Linux.

#### 2.4.2 Threads

In the Linux kernel, each thread is represented by a set of variables embedded in a structure (**struct task\_struct**). These variables include the thread's address space, a pointer to its parent, file descriptors, pending signals, as well as statistics such as its execution time or the number of bytes accessed through I/O devices. From now on, we only focus on scheduler-related attributes.

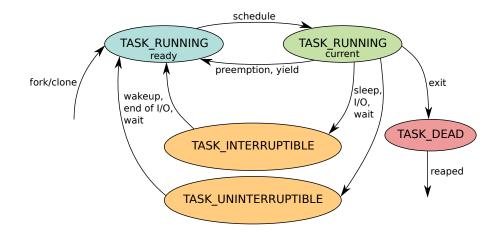

From the scheduler subsystem's point of view, a thread is defined by its *state*. As seen in Section 2.3.2, these states can be seen as states of a finite state machine while scheduler functions can be seen as transitions. Figure 2.6 shows the finite state machine used in Linux. Although similar to the three-state thread model presented earlier, there exists some differences between the generic and the Linux model.

Runnable threads in the runqueue are in the TASK\_RUNNING state, tagged as ready in the figure. This is the equivalent of the READY state. The currently running thread is also in the TASK\_RUNNING state, tagged as current. This is equivalent to the RUNNING state. Transitioning from the former to the latter is done when the schedule() function is called, while the reverse transition is due to preemption (exhausted time slice or higher priority thread available) or yielding.

Threads in the TASK\_INTERRUPTIBLE state sleep until they are woken up, e.g. end of I/O or reception of a non-masked signal, whereas threads in the TASK\_UNINTERRUPTIBLE state behave in the same way except they ignore signals altogether. Going into one of these states means that a RUNNING thread went to sleep or is waiting for a resource (I/O, lock) to be available. When the resource becomes available, the thread goes back to a READY state, ready to use the CPU.

The TASK\_DEAD state is a temporary state used at thread termination. When in this state, the thread will no longer be executed. Its metadata are kept in memory until its parent thread *reaps* it. This is necessary to pass the return value of a terminated thread or to know how this

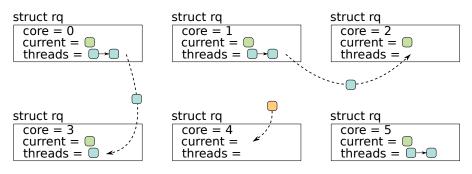

**Figure 2.7:** Distributed design of the Linux scheduler, with threads migrating to balance load (core  $0 \rightarrow 3$  and  $1 \rightarrow 2$ ), or waking up on idle cores (core 4).

thread terminated, e.g. normally or because of an exception. Threads in this state are colloquially called *zombies*.

Each thread also has policy-specific variables for each scheduling policy in Linux. For example, the real-time policy SCHED\_DEADLINE stores a *deadline* and a *period*. On the other hand, the SCHED\_OTHER policy computes a *load* that reflects the weight a thread has on the computing resources. These policy-specific variables will be discussed in more details in the sections describing each policy.

#### 2.4.3 Runqueues

The Linux scheduler, just as the kernel in general, was originally designed for single-core machines. All subsystems were designed in a centralized way, with no concurrent accesses to scheduling data in mind.<sup>12</sup> When SMP support was introduced in 2006 with Linux v2.6, a Big Kernel Lock (BKL) was used for mutual exclusion. This solution scaled poorly and led kernel developers to move from this BKL to more fine-grained locking and designs that were able to scale with the number of cores.<sup>13</sup>

For the thread scheduler, this materialized by making it a distributed system: each core maintains a *runqueue* (a **struct rq**) that contains, among other things, the currently running thread and a set of runnable threads that are waiting for the CPU resource. Figure 2.7 shows this distributed design. Each core takes its scheduling decisions locally, as if it was operating on a single core machine. This reduces contention on locks, since each runqueue has its own lock and locking multiple runqueues is rarely needed. This distributed scheduler architecture also favors cache locality by design.

However, such a distributed design can lead to situations where work is unequally distributed among cores, as seen in Figure 2.7. To mitigate this, threads can be migrated by the scheduler from one core to another. This can happen because of particular thread-related events, e.g. thread creation or unblock after an I/O, or because of scheduler-triggered actions, e.g. periodic load balancing. <sup>12</sup> On single core machines, disabling interrupts is enough to avoid concurrency problems between threads.

<sup>13</sup> This BKL removal process took 9 years to complete [16, 37].

#### 2.4.4 The Scheduling Class API

The Linux kernel provides an internal application programming interface (API) that allows developers to implement a thread scheduler in the kernel: *scheduling classes*. It consists of a set of functions to implement, described in Table 2.1. The core code of the scheduler subsystem<sup>14</sup> does all the generic work that is common to all scheduling policies. This includes acquiring and releasing locks, changing thread state, enabling and disabling interrupts, ... Outside of this generic code, each policy has its own code that implements different scheduling algorithms.

To illustrate the interactions between generic and policy-specific code, we describe the creation of a thread, be it with the fork() or clone() system call. First, the data structures representing the parent thread's state are copied to create the child thread. This includes the **struct task\_struct**, the file descriptors, the page table address for multithreaded applications, etc... Attributes are then correctly initialized, e.g. the PID and PPID. Note that by default, a thread inherits its parent's scheduling policy. These operations are performed by the copy\_process() function. When all is correctly set up, the thread scheduler is now able to make this new thread runnable.

The wake\_up\_new\_task() function is responsible for making the newly created thread runnable. Let T be this newly created thread and  $S_T$  its associated scheduling class (e.g. SCHED\_OTHER, SCHED\_FIFO), here is the initial wakeup algorithm:

- 1. Lock *T* and disable interrupts.

- Call the select\_task\_rq() function of S<sub>T</sub> in order to choose on which core T will be enqueued. Let this core be C<sub>dst</sub>.

- 3. Lock  $C_{dst}$ .

- 4. Call the enqueue\_task() function of  $S_T$  in order to actually put T in the runqueue of  $C_{dst}$ .

- 5. Unlock  $C_{dst}$ , T and enable interrupts.

Only steps 2 and 4 involve policy-specific code. The rest is provided as is by the scheduler subsystem.

Providing this internal API allows developers to implement thread schedulers without reimplementing generic code and also helps minimizing the number of bugs. Indeed, developing in the Linux kernel is difficult, and it is hard to have a big picture understanding of all mechanisms involved. This lack of understanding could lead developers to do things improperly, such as incorrectly handling interrupts or locks.

<sup>14</sup> Defined in the kernel/sched/core.c file.

| Function                             | Description                                                                                             |

|--------------------------------------|---------------------------------------------------------------------------------------------------------|

| <pre>enqueue_task(rq, t)</pre>       | Add thread t to runqueue rq                                                                             |

| <pre>dequeue_task(rq, t)</pre>       | Remove thread t from runqueue rq                                                                        |

| yield_task(rq)                       | Yield the currently running thread on the CPU of rq                                                     |

| <pre>check_preempt_curr(rq, t)</pre> | Check if the currently running thread of rq should be pre-<br>empted by thread t                        |

| <pre>pick_next_task(rq)</pre>        | Return the next thread that should run on rq                                                            |

| <pre>put_prev_task(rq, t)</pre>      | Remove the currently running thread t from the CPU of rq                                                |

| <pre>set_next_task(rq, t)</pre>      | Set thread t as the currently running thread on the CPU of rq                                           |

| balance(rq)                          | Run the load balancing algorithm for the CPU of rq                                                      |

| <pre>select_task_rq(t)</pre>         | Choose a new CPU for the waking up/newly created thread t                                               |

| task_tick(rq)                        | Called at every clock tick on the CPU of rq if the currently running thread is in this scheduling class |

| task_fork(t)                         | Called when thread t is created after a fork()/clone() system call                                      |

| task_dead(t)                         | Called when thread t terminates                                                                         |

**Table 2.1:** Scheduling class API in the Linux v5.7 kernel. Only a subset of functions are presented and some function parameters were omitted for conciseness.

CAVEATS OF THIS INTERNAL API. Despite all its benefits, the scheduling class internal API still suffers some problems. First, the behavior of every function of the API is not strictly defined. For example, the enqueue\_task() implementations currently available throughout the kernel can enqueue one, multiple or no thread in the runqueue. This means that in this function, anything can happen. This greatly limits the possibilities for static analysis tools or formalization in order to prove the correctness of the scheduler.

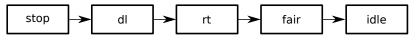

META-SCHEDULER. As stated previously, Linux complies with a large portion of the POSIX standards, including parts involving thread scheduling. To this end, it implements multiple scheduling policies that we describe in the following sections. However, this also means that if multiple policies have a runnable thread, a choice must be made by Linux to determine which policy has the highest priority. Linux chooses a simple fixed-priority list to determine this order. Figure 2.8 shows this priority list. When a thread is scheduled out, the scheduler subsystem will iterate over this list and call the pick\_next\_task() function of each class until a thread is returned.

Figure 2.8: Priority list of Linux's scheduling classes.

#### 2.5 GENERAL-PURPOSE OPERATING SYSTEM SCHEDULERS

In this section, we present multiple general-purpose schedulers implemented in production OSs like Linux or Windows. We emphasize more on Linux since the contributions presented in this thesis are implemented on this OS. We present historical schedulers of Linux as well as the current one, CFS. We also present some competing schedulers that live outside the Linux mainline code.

#### 2.5.1 Former Linux Schedulers

For a rather long time, Linux used a very simple scheduler, with the idea that thread scheduling was easy and not a problem.

Let's face it — the current scheduler has the same old basic structure that it did almost 10 years ago, and yes, it's not optimal, but there really aren't that many real-world loads where people really care. I'm sorry, but it's true.

And you have to realize that there are not very many things that have aged as well as the scheduler. Which is just another proof that scheduling is easy.

— Linus Torvalds, 2001 [173]

Reality proved to be a little bit different, and the Linux scheduler became a performance problem for many users. This led to multiple rewrites of the scheduler over the years. We now present the multiple schedulers that existed in Linux before the current one.

# 2.5.1.1 Round-Robin Scheduler

The first versions of Linux used a simple round-robin scheduler. Runnable threads are stored in a linked list and each thread is assigned a fixed time slice. When a thread completes its time slice or switches to a blocked state, the next thread in the list is elected. Unsurprisingly, this design works poorly in an interactive setup such as a desktop computer. Indeed, I/O-bound threads usually run very briefly and very frequently, i. e. they do not use their time slice, while CPU-bound threads use their whole time slice. This leads to unfairness between these two types of threads with a round-robin policy.

This information is extracted from the source code of earlier Linux versions. A full reconstruction of the git history of the Linux project is available at: https://github.com/mpe/linux-fullhistory.

**Figure 2.9:** Data structures of the O(n) scheduler in Linux.

#### 2.5.1.2 The O(n) Scheduler

To solve the unfairness between batch and interactive threads, the Linux community introduced the O(n) scheduler in Linux v2.4 in 2001. The overall idea is that the scheduler assigns a time slice to each thread on the system. To do this, the scheduler divides time in *epochs*. At the end of each epoch, the scheduler reallocates a time slice to each thread and gives a bonus to threads that did not consume their whole time slice during the previous epoch.<sup>15</sup> All threads, runnable or not, are stored in a linked list, the tasks list. Runnable threads are also part of the runnable list, as shown in Figure 2.9. When the OS needs to choose a new thread to run, the O(n) scheduler iterates through the runnable list and computes a *goodness* score for each thread. This goodness is computed with various metrics, such as the *nice* value or the time already consumed from its allocated time slice. The thread with the highest goodness is the one that will be given access to the core.

Thanks to the goodness metric, this new scheduler was quite fair between threads, and interactivity was no longer penalized. However, the major caveat of this new scheduler is the algorithmic complexity of its operations. While the previous scheduler performed all operations in constant time, this new scheduler iterates through all runnable threads when choosing a new thread to run. This meant that the duration of the election depended on the number of runnable threads, hence the name of this scheduler, O(n).

#### 2.5.1.3 The O(1) Scheduler

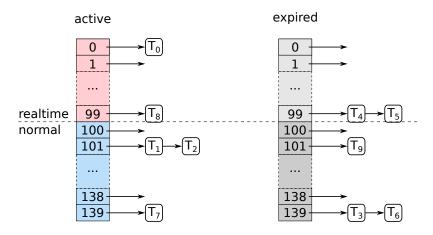

With the advent of multi-core architectures and multithreaded programming, the complexity of the O(n) scheduler became prohibitive. The O(1) scheduler, as well as proper support for SMP architectures, was introduced in 2003 with Linux v2.6 to solve this problem. This description is derived from code reading and from the excellent *Linux Kernel Development* (2<sup>*nd*</sup> *Edition*) book from Robert Love [111].

As shown by Figure 2.10, a runqueue consists of two *priority arrays*, i. e. arrays of lists, with 140 entries each: the *active* and *expired* arrays. Each entry corresponds to a different priority level: o to 99 are realtime priorities and 100 to 139 are normal priorities.<sup>16</sup> When a new thread must be elected by the scheduler, the highest priority thread in the *active* array is selected. In our example,  $T_0$  would be the first thread to be elected. When a thread uses all its time slice, it is moved <sup>15</sup> The bonus is equal to half the time remaining in the thread's time slice.

<sup>16</sup> These 40 levels of normal priorities are mapped to the nice value that ranges from -20 to 19.

**Figure 2.10:** Data structures of the O(1) scheduler in Linux.

| Nice | Time slice |

|------|------------|

| +19  | 5 ms       |

| 0    | 100 ms     |

| -20  | 800 ms     |

**Table 2.2:** Time slice allocations in O(1).

from the *active* to the *expired* priority array, its time slice is recomputed, and another thread is scheduled. When the *active* array is empty, both arrays are swapped: *expired* becomes *active* and vice versa. The time slice allocated to a thread depends on its priority, as shown by Table 2.2. This new design allows for good balance between interactive and batch threads, thanks to priorities, and does so while maintaining a good O(1) algorithmic complexity, thanks to priority arrays.

The SMP support in the scheduler consists of mov-SMP SUPPORT. ing from a centralized runqueue to distributed runqueues, each core scheduling threads locally without knowledge of other cores. This distributed scheduler architecture brings new challenges. From now on, since each core only schedules the threads in its runqueue, threads can be asymmetrically distributed among cores. One core could have 10 threads to schedule while another one could have only one single thread to schedule, leading to unfairness between threads depending on the core they are placed on. To solve this problem, the scheduler performs load balancing by migrating threads between cores in order to even the number of threads of all cores. This balancing is performed on two occasions: (i) when a core becomes idle, i. e. no runnable thread is locally available, (ii) periodically, every millisecond when the system is idle, every 200 ms otherwise. Load balancing is done with a work stealing approach: each core does its own balancing and tries to steal threads from the busiest core on the system. To reduce the cost of this balancing and the number of migrations, balancing has some constraints: threads are migrated only if the imbalance between cores exceeds 25%, and cache-hot threads, i. e. threads in the active array, are less likely to be migrated than other threads, i.e. threads in the *expired* array.

## 2.5.2 Completely Fair Scheduler

The Completely Fair Scheduler (CFS) is the default scheduler in Linux since 2007, with version 2.6.23. The general idea behind this scheduler is to "model an ideal, precise multi-tasking CPU on real hardware" [29]. The meaning behind this is that CFS aims at emulating an ideal CPU that would execute all runnable threads in parallel, allocating each thread the exact same computing power simultaneously. For example, if 4 threads are runnable, each thread should be allocated 25% of the CPU power at all times. However, since real hardware provides a finite number of cores that can simultaneously run one thread each, CFS has to model such an ideal hardware. We will first describe how CFS manages the allocation of CPU time to threads, and then detail the thread placement strategy of CFS. Most of the information of this section is extracted from the Linux v5.4 kernel source code and from Robert Love's excellent book, Linux Kernel Development, Third Edition [112].

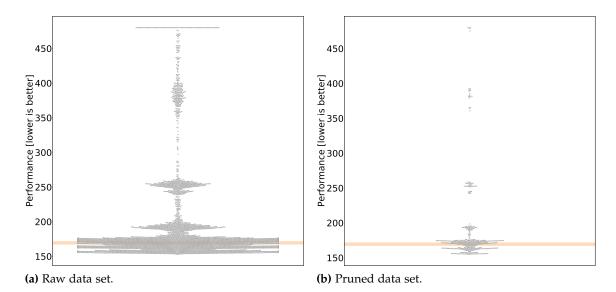

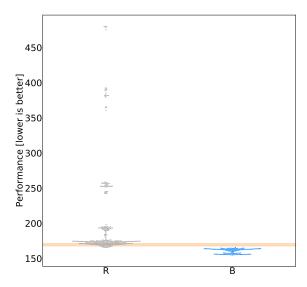

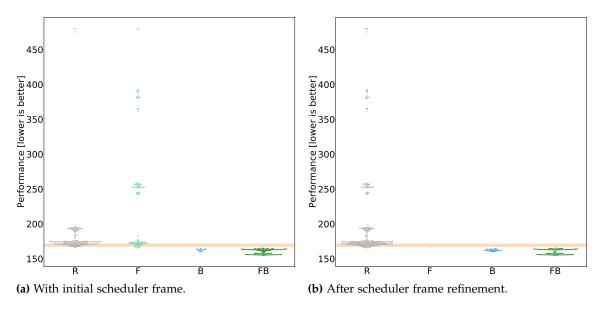

## 2.5.2.1 Election in CFS